| XADC 原理及Xilinx FPGA XADC IP | 您所在的位置:網(wǎng)站首頁(yè) › 屬狗住幾樓好 › XADC 原理及Xilinx FPGA XADC IP |

XADC 原理及Xilinx FPGA XADC IP

|

目錄 文章目錄 前言 一、XADC是什么 一、XADC的引腳介紹 二、XADC端口介紹 四、XADC的寄存器接口 五、時(shí)序圖 六、Vivado IP核調(diào)用仿真 調(diào)用IP核 仿真查看 前言? ? ? ? XADC這個(gè)詞,剛?cè)ス旧习嗟臅r(shí)候就聽(tīng)到老同事常常提到,但是自己不知道是啥玩意。后面自己下來(lái)學(xué)習(xí)才對(duì)它有一定的了解; 提示:以下是本篇文章正文內(nèi)容,下面案例可供參考 一、XADC是什么

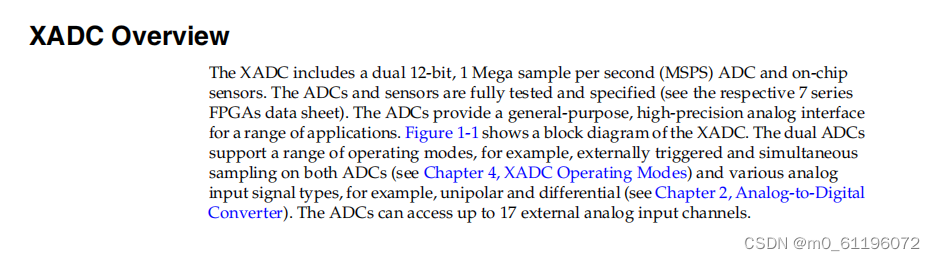

?? ? ? ? 參考的XLINX的ug480_7Series_XADC手冊(cè),它的涵義概括:XADC包括一個(gè)雙16位(有效12位),1兆樣本每秒(MSPS)ADC和片上傳感器。adc為一系列應(yīng)用提供了通用的高精度模擬接口,最多可訪問(wèn)17個(gè)外部模擬輸入通道。。圖1-1顯示了XADC的方框圖。 ?????????結(jié)合圖片來(lái)看一下  圖片1-1

圖片1-1

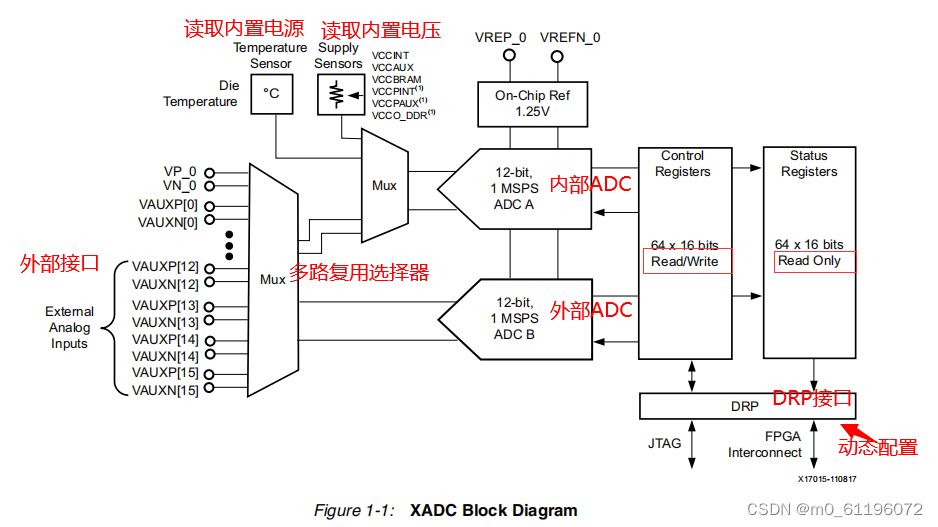

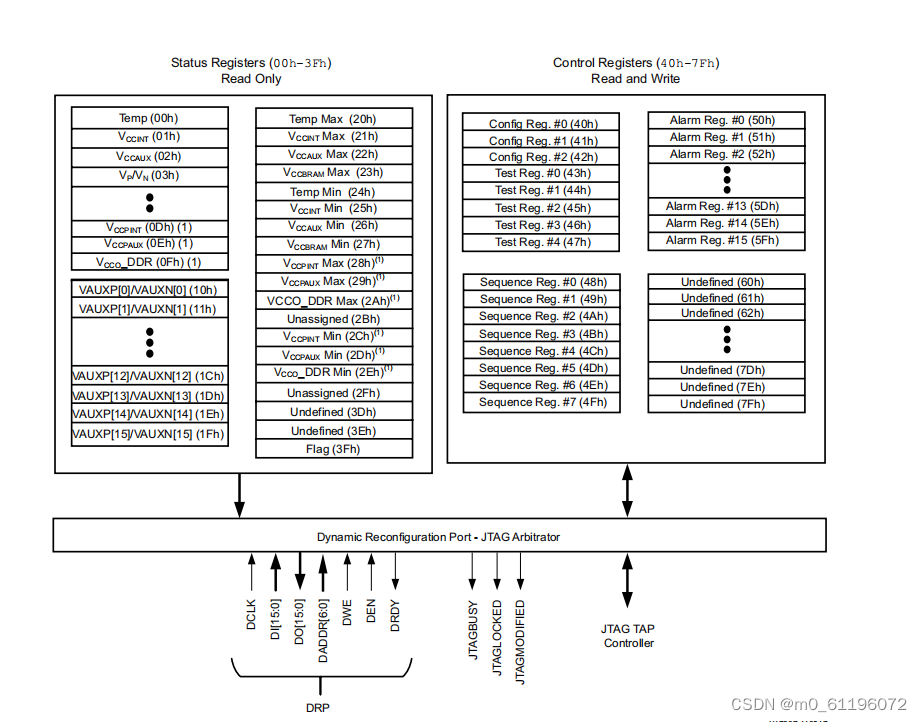

與圖片1-1相關(guān)注釋僅限??Zynq?7000??SoC??器件;??? ? ? ?? ? ? ? ??XADC還包括多個(gè)片上傳感器,支持測(cè)量片上電源電壓和芯片溫度。ADC??轉(zhuǎn)換數(shù)據(jù)存儲(chǔ)在稱為狀態(tài)寄存器的專用寄存器中。這些寄存器可通過(guò)FPGA?互連使用稱為動(dòng)態(tài)重配置端口??(DRP)??的16位同步讀寫(xiě)端口訪問(wèn)ADC??轉(zhuǎn)換數(shù)據(jù)也可 以通過(guò)??JTAG??TAP??訪問(wèn),無(wú)論是在配置之前(預(yù)配置)還是配置之后。對(duì)于??JTAG??TAP,用戶不需要例化??XADC,使用有FPGA??JTAG??基礎(chǔ)設(shè)施的專用接口。如后文所述,如果??XADC??未在設(shè)計(jì)中例化,則該器件將在預(yù)定義模式(稱為默認(rèn)模式)下運(yùn)行,該模式監(jiān)控片上溫度和電源電壓。 ? ? ? ?? 一、XADC的引腳介紹????????VCCADC_0:這是??XADC??中??ADC??和其他模擬電路的模擬電源引腳。它可以連接到到1.8V??VCCAUX 電源;但是,在混合信號(hào)系統(tǒng)中,電源應(yīng)連接到單獨(dú)的??1.8V??模擬(如果使用); ????????GNDADC_0:接地; ????????VREFP_0:參考電壓輸入;該引腳可以綁定到一個(gè)外部的1.25V,以獲得adc的最佳性能。它應(yīng)被視為一個(gè)模擬信號(hào),與VREFN信號(hào)一起提供一個(gè)差分的1.25V電壓。通過(guò)將此引腳連接到GNDADC,片上參考源被激活。如果沒(méi)有提供外部引用,則該引腳應(yīng)該始終連接到GNDADC; ????????VREFN_0:同上; ????????VP_0:專用模擬輸入;這是專用差動(dòng)模擬輸入通道(VP/VN)的正輸入端。模擬輸入信道非常靈活,并支持多種模擬輸入信號(hào)類型。如果不使用,該引腳應(yīng)連接到GND。 ????????VN_0:同上; ? ? ? ? _AD0P_ to _AD15P_:這些是多功能引腳,可以支持模擬輸入,或者可以用作常規(guī)數(shù)字輸入/輸出(參見(jiàn)圖1-1)。這些引腳支持差動(dòng)輔助模擬輸入通道(VAUXP/VAUXN)的多達(dá)16個(gè)正輸入端子。模擬輸入信道非常靈活,并支持多種模擬輸入信號(hào)類型。當(dāng)不被用作模擬輸入時(shí),這些引腳可以像任何其他數(shù)字I/O一樣被處理; ????????_AD0N_ to _AD15N_:同上。 ???????? 二、XADC端口介紹????????  圖片2-1

圖片2-1

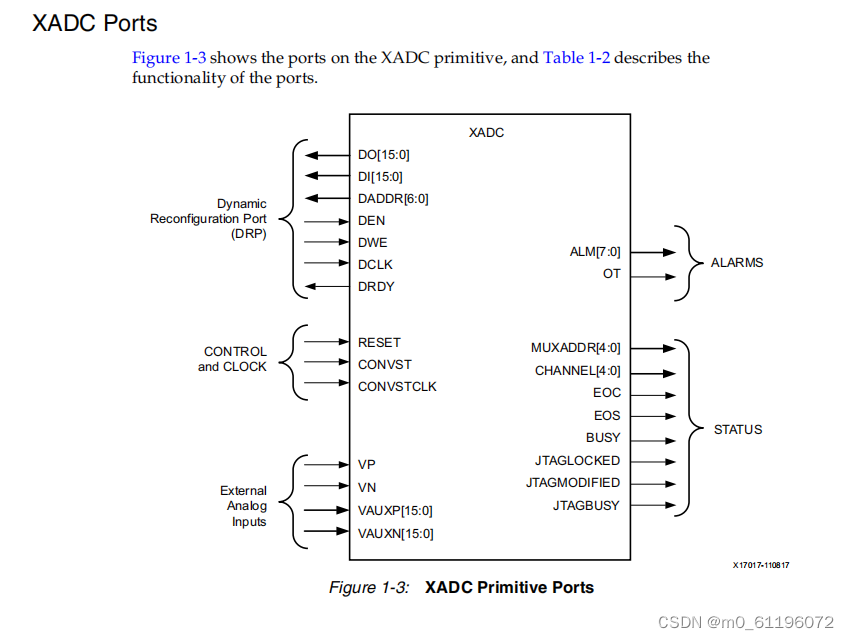

以DRP的端口說(shuō)明(DRP的端口數(shù)據(jù)相比于AXI4簡(jiǎn)單一點(diǎn)): ????????DI[15:0]:(I)為DRP的輸入數(shù)據(jù)總線; ????????DO[15:0]:(O)DRP的輸出數(shù)據(jù)總線; ????????DADDR[6:0]:(I)?為DRP的地址總線; ? ? ? ??DEN:(I)為DRP啟用信號(hào)?;? ?? ????????DWE:(I)為DRP啟用寫(xiě)功能; ????????DCLK:(I)針對(duì)DRP的時(shí)鐘輸入; ????????DRDY:(O)為DRP提供相應(yīng)的數(shù)據(jù)準(zhǔn)備信號(hào); ????????RESET:(I)為XADC控制邏輯的異步復(fù)位信號(hào)。當(dāng)DCLK停止時(shí),重置將被同步終止到DCLK或內(nèi)部配置時(shí)鐘; ????????CONVST:(I)轉(zhuǎn)換開(kāi)始輸入; ????????CONVSTCLK:(I)轉(zhuǎn)換啟動(dòng)時(shí)鐘輸入。此輸入端已連接到一個(gè)時(shí)鐘網(wǎng)。與CONVST一樣,該輸入控制ADC 輸入上的采樣瞬間,并且僅在事件模式定時(shí)中使用。這個(gè)輸入來(lái)自于FPGA邏輯中的本地時(shí)鐘分配網(wǎng)絡(luò)。因此,為了實(shí)現(xiàn)對(duì)采樣瞬間(延遲和抖動(dòng))的最佳控制,一個(gè)全局時(shí)鐘輸入可以被用作CONVST源; ????????VP , VN:(I)一個(gè)專用的模擬輸入對(duì)。XADC有一對(duì)專用的模擬輸入引腳,提供一個(gè)差分模擬輸入。當(dāng)使用XADC特性進(jìn)行設(shè)計(jì),但不使用VP和VN的專用外部通道時(shí),您應(yīng)該將VP和VN同時(shí)連接到模擬地面上; ????????VAUXP[15:0], VAUXN[15:0]:(I )16對(duì)輔助模擬輸入對(duì)。除了專用的差分模擬輸入外,XADC還可以通過(guò)配置數(shù)字輸入/O為模擬輸入來(lái)訪問(wèn)16個(gè)差分模擬輸入。這些輸入也可以通過(guò)JTAG端口; ????????ALM[0]:(O)溫度傳感器報(bào)警輸出。 ????????ALM[1]:(O)VCCINT傳感器報(bào)警輸出。 ????????ALM[2]:(O)VCCAUX傳感器報(bào)警輸出 ????????ALM[3]:(O)VCCBRAM傳感器報(bào)警輸出。 ????????ALM[4]:(O)VCCPINT傳感器報(bào)警輸出。 ????????ALM[5]:(O)VCCPAUX傳感器報(bào)警輸出。 ????????ALM[6]:(O)VCCO_DDR傳感器報(bào)警輸出 ????????ALM[7]:(O)總線的邏輯或。可用于標(biāo)記任何警報(bào)的發(fā)生。 ????????OT:(O)超溫報(bào)警輸出。 ????????MUXADDR[4:0]: (O)這些輸出在外部多路復(fù)用器模式下使用。它們表示要轉(zhuǎn)換的序列中的下一個(gè)通道的地址。它們?yōu)橥獠慷嗦窂?fù)用器提供通道地址; ????????CHANNEL[4:0]:(O)通道選擇輸出。對(duì)于當(dāng)前ADC轉(zhuǎn)換的ADC輸入MUX通道選擇在ADC轉(zhuǎn)換結(jié)束時(shí)被放置在這些輸出上。 ????????EOC:(O)轉(zhuǎn)換信號(hào)結(jié)束。當(dāng)測(cè)量值被寫(xiě)入狀態(tài)寄存器時(shí),該信號(hào)在ADC轉(zhuǎn)換結(jié)束時(shí)轉(zhuǎn)換到高電平 ????????EOS:(O)序列結(jié)束。當(dāng)從自動(dòng)通道序列中的最后一個(gè)通道的測(cè)量數(shù)據(jù)被寫(xiě)入狀態(tài)寄存器時(shí),該信號(hào)轉(zhuǎn)換到高電平; ????????BUSY:(O)ADC忙信號(hào)。這個(gè)信號(hào)在ADC轉(zhuǎn)換過(guò)程中轉(zhuǎn)換到高電平; ????????JTAGLOCKED:(O)表示JTAG接口已發(fā)出DRP端口鎖定請(qǐng)求。該信號(hào)也用于指示DRP準(zhǔn)備訪問(wèn)(當(dāng)?shù)蜁r(shí)); ????????JTAGMODIFIED:(O)用于指示已發(fā)生JTAG寫(xiě)入DRP。 ????????JTAGBUSY:(O)用于指示正在進(jìn)行的JTAG DRP事務(wù)。 注:VCCINT(內(nèi)核電壓),VCCAUX(輔助電壓),VCCRAM(RAM塊電壓),VCCO(IO電壓) 四、XADC的寄存器接口? ? ? ? 圖片4-1說(shuō)明了XADC寄存器接口。寄存器接口中的所有寄存器都可以通過(guò)動(dòng)態(tài)重新配置端口(DRP)進(jìn)行訪問(wèn)。DRP可以通過(guò)FPGA邏輯端口或JTAG TAP進(jìn)行訪問(wèn)。DRP允許訪問(wèn)最多128個(gè)16位寄存器(DADDR[6:0] = 00h到7Fh)。前64個(gè)訪問(wèn)位置(DADDR[6:0] = 00h到3Fh)是只讀的,并包含ADC測(cè)量數(shù)據(jù)。這些寄存器被稱為狀態(tài)寄存器。控制寄存器位于40h到7Fh的地址處,并且可通過(guò)DRP可讀或可寫(xiě)。  圖片4-1

圖片4-1

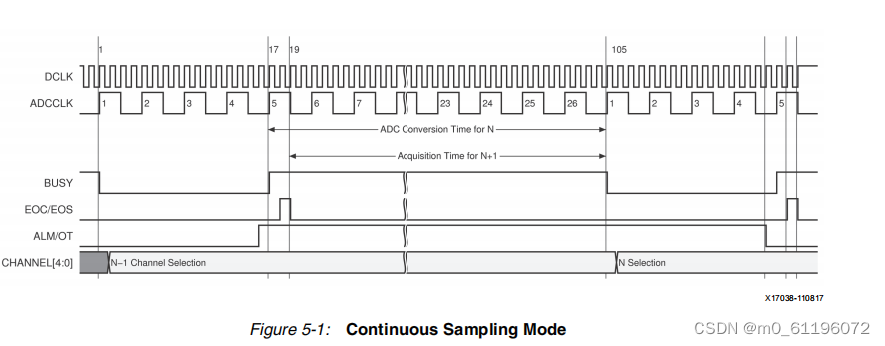

? ? ? ?? Status Registers和Control Registers具體內(nèi)容查閱手冊(cè) 五、時(shí)序圖連續(xù)采樣  圖片5-1

圖片5-1

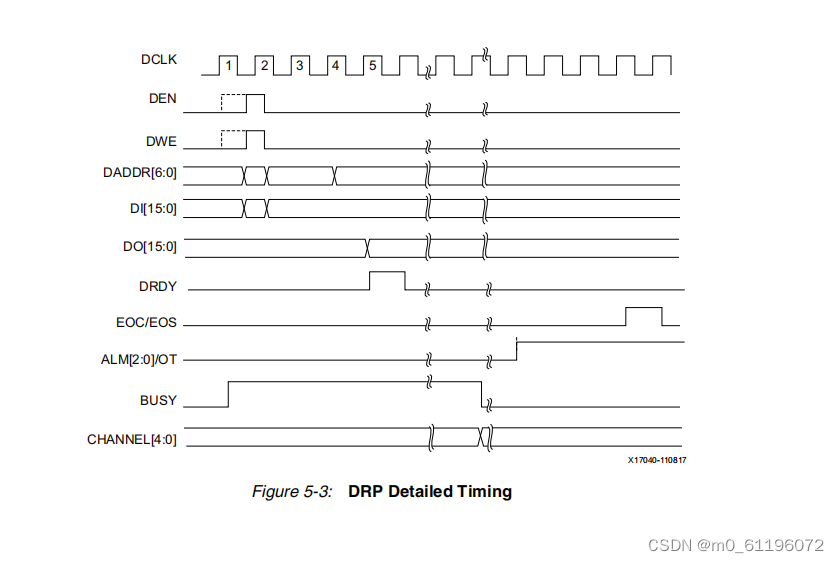

?動(dòng)態(tài)重新配置端口(DRP)  圖片5-2

六、Vivado IP核調(diào)用仿真

調(diào)用IP核

圖片5-2

六、Vivado IP核調(diào)用仿真

調(diào)用IP核

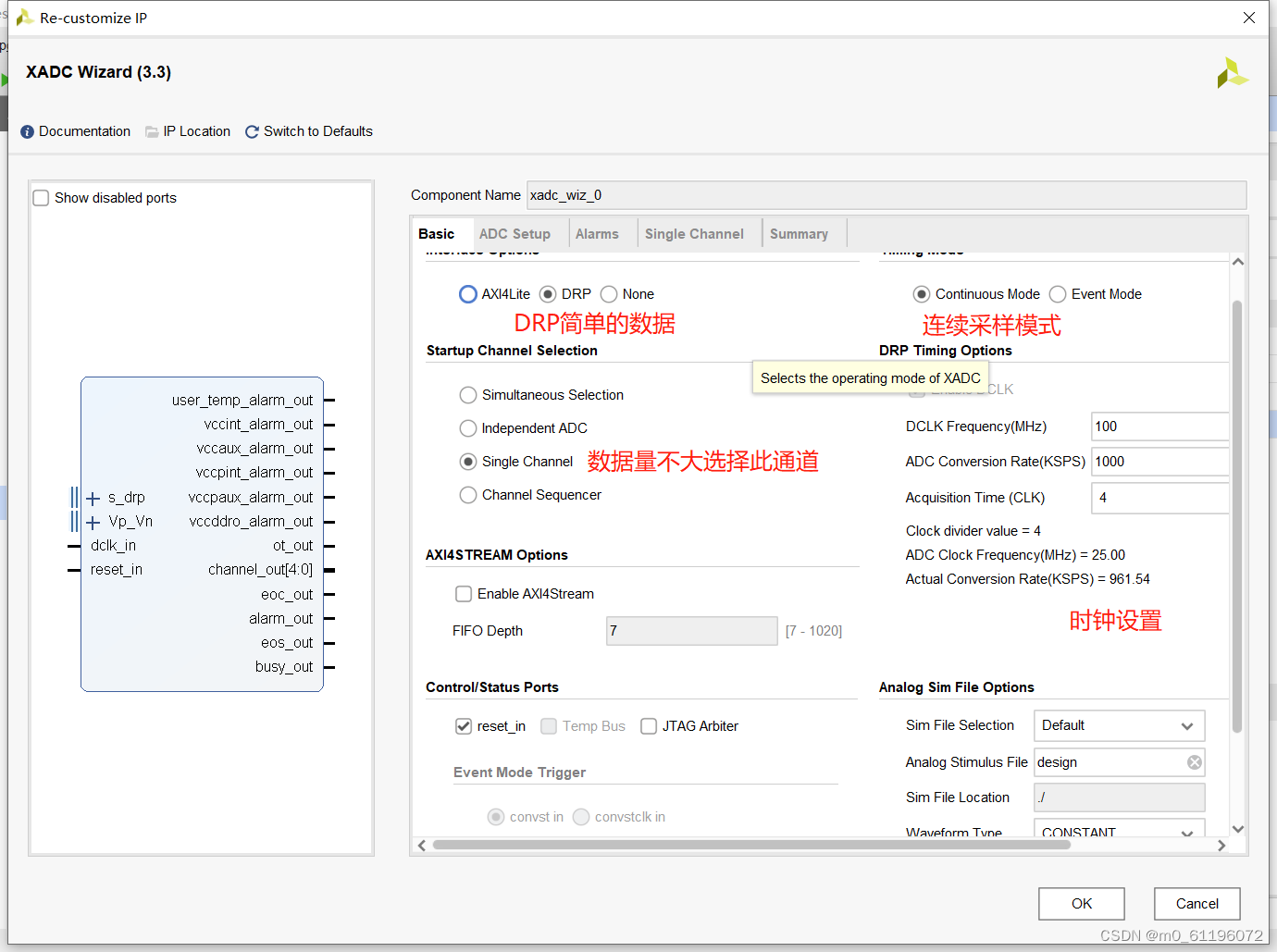

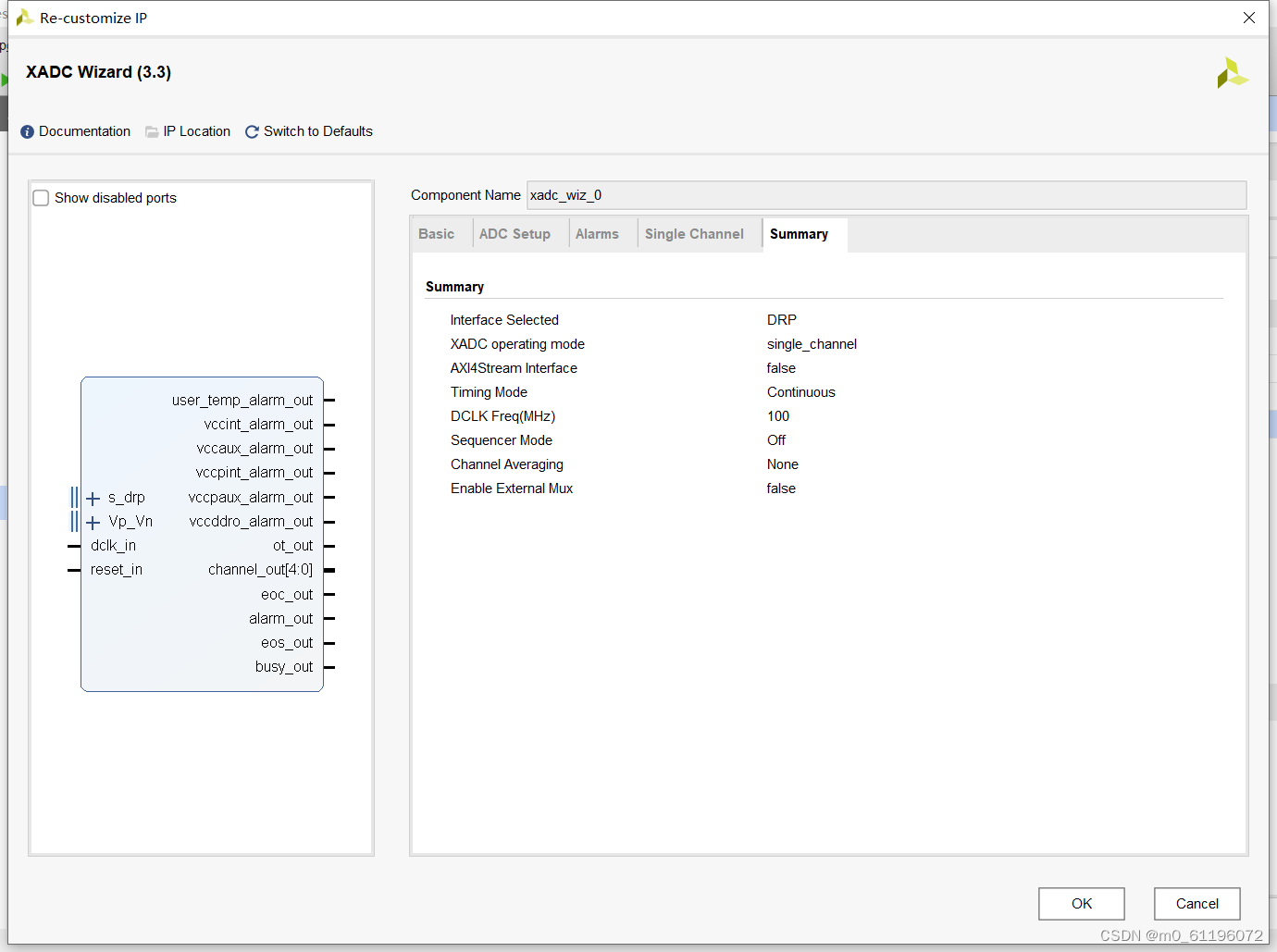

圖片6-1

圖片6-1

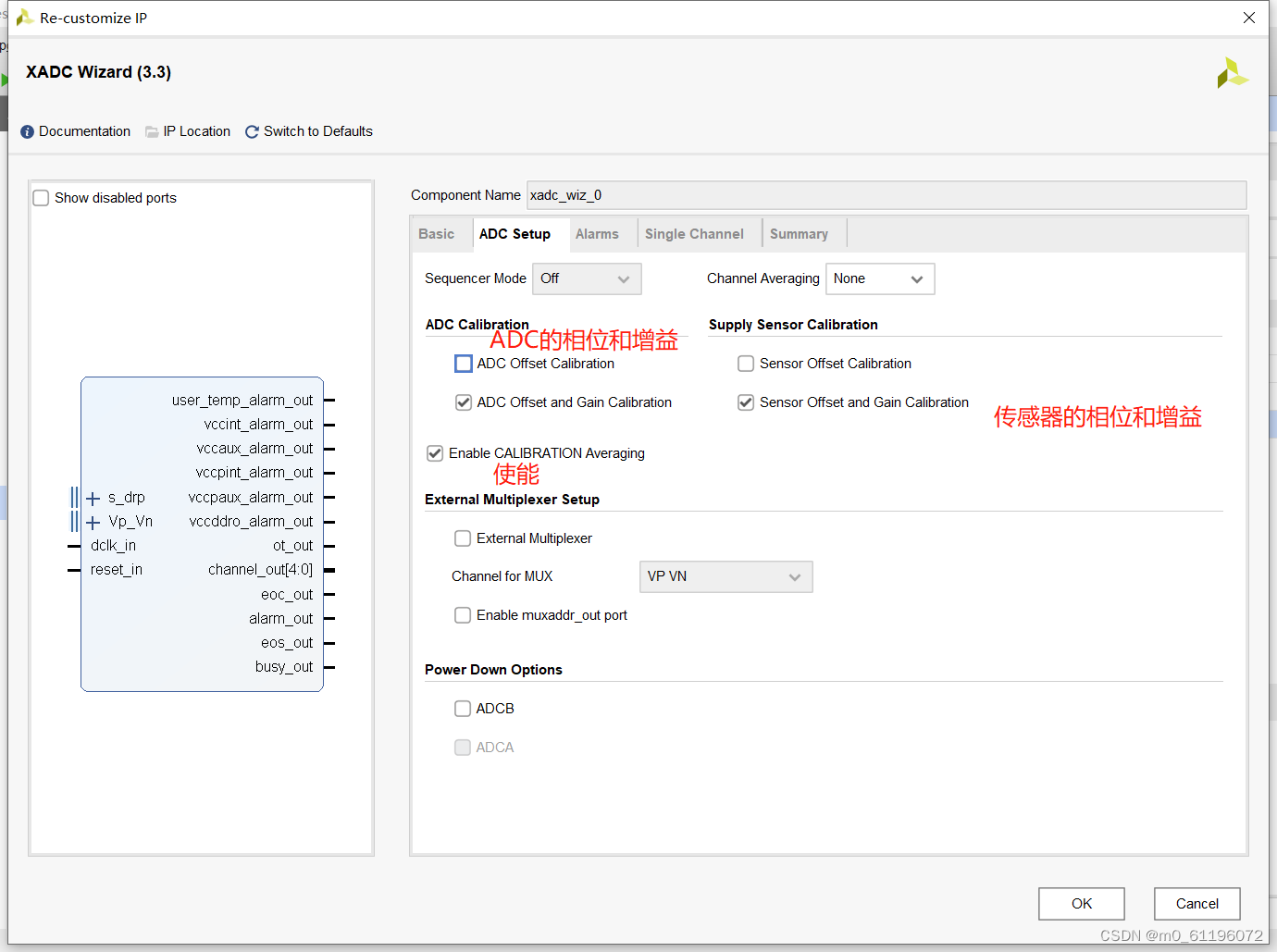

圖片6-2

圖片6-2

6-3

6-3

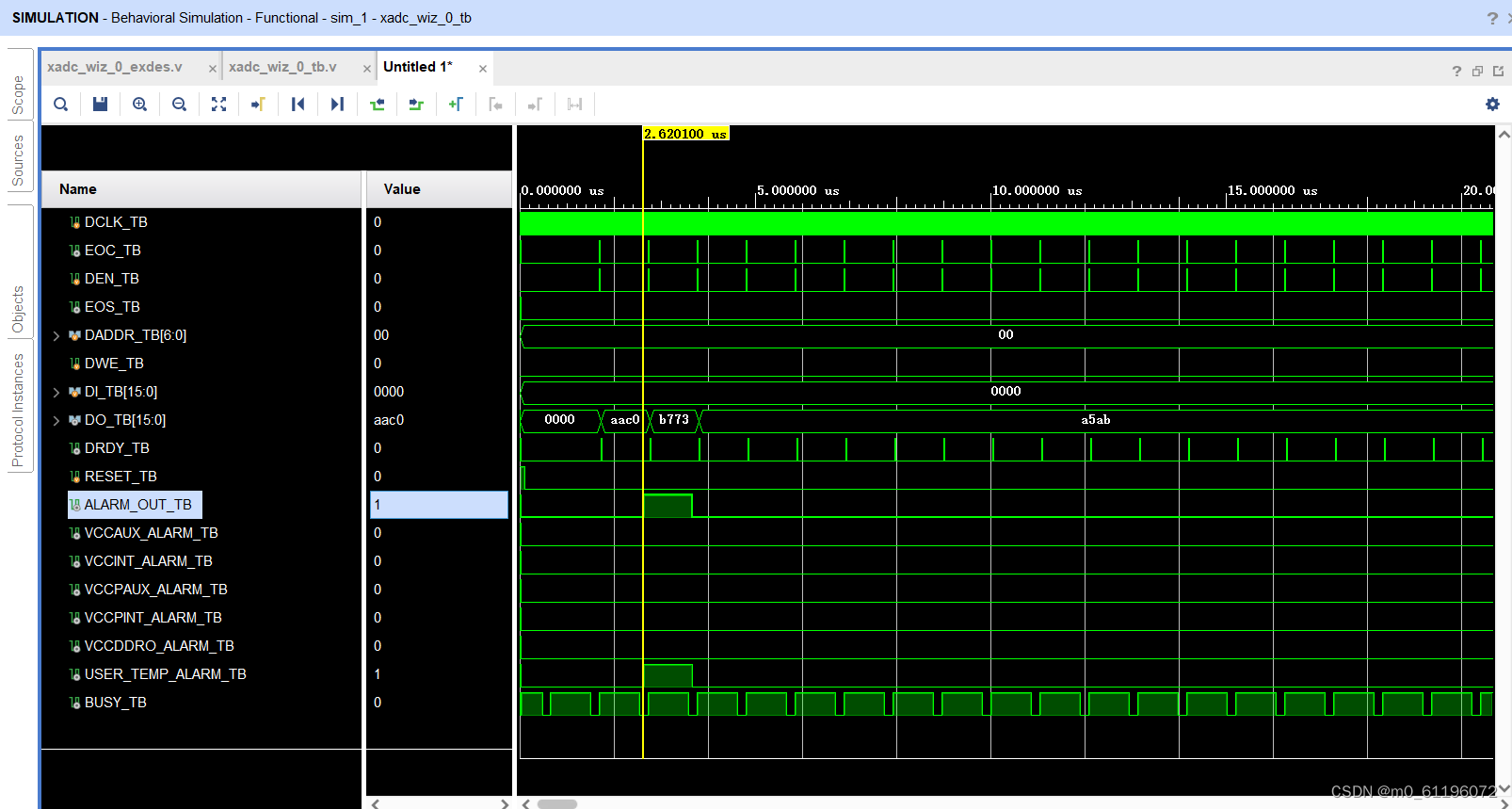

?PS:默認(rèn)選擇,簡(jiǎn)單的時(shí)序,熟悉在深入 仿真查看 ?PS:結(jié)合時(shí)序圖查看仿真更多準(zhǔn)確詳細(xì)信息請(qǐng)查閱手冊(cè)u(píng)g480和pg091

?PS:結(jié)合時(shí)序圖查看仿真更多準(zhǔn)確詳細(xì)信息請(qǐng)查閱手冊(cè)u(píng)g480和pg091

|

【本文地址】

| 今日新聞 |

| 推薦新聞 |

| 專題文章 |