| DDR3和mig的介紹 | 您所在的位置:網(wǎng)站首頁 › 夫妻屬蛇可以生虎寶寶嗎女孩子 › DDR3和mig的介紹 |

DDR3和mig的介紹

|

作者:OpenSLee,來源:FPGA開源工作室 FPGA開源工作室將通過五篇文章來給大家講解xilinx FPGA 使用mig IP對DDR3的讀寫控制,旨在讓大家更快的學(xué)習(xí)和應(yīng)用DDR3。 本實驗和工程基于Digilent的Arty Artix-35T FPGA開發(fā)板完成。 軟件使用Vivado 2018.1。 第一篇:DDR3和mig的介紹 1 DDR3介紹 以鎂光的MT41K128M16為例來介紹DDR3。

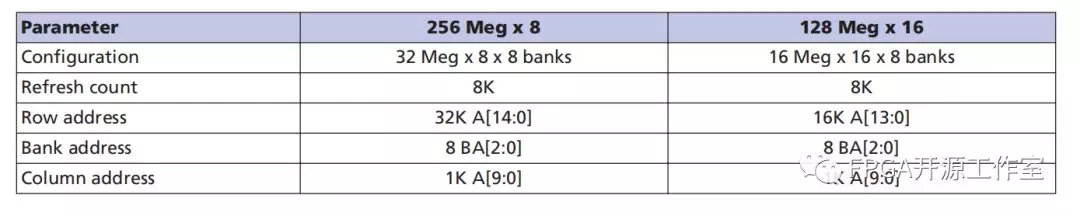

通過以上信息我們即可知道DDR3的內(nèi)存容量,Row,Column和Bank的地址位寬。開發(fā)板選用的MT41K128M16 DDR3的容量為16Megx16x8banks=2048Mb=2Gb。 1.1 DDR3命名

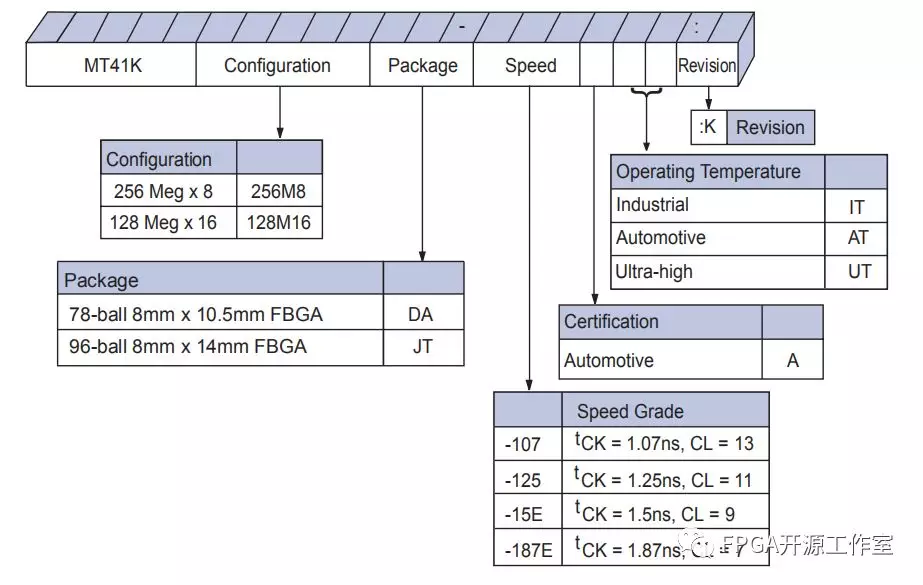

我們通過Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封裝,速度等級等信息。 1.2 DDR3的內(nèi)部結(jié)構(gòu)

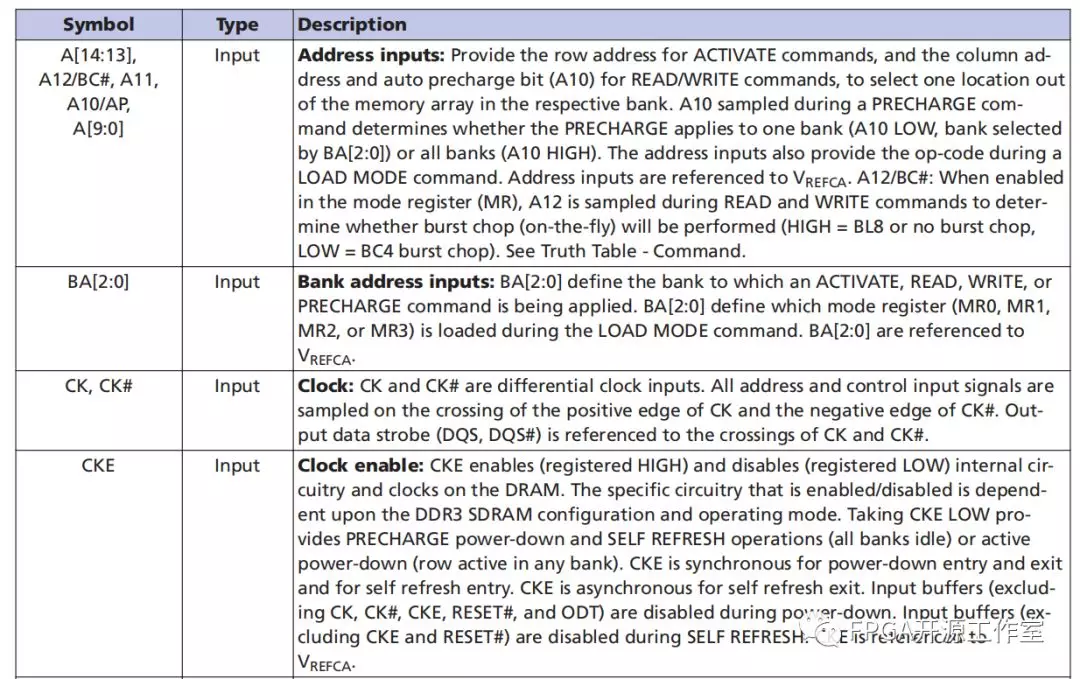

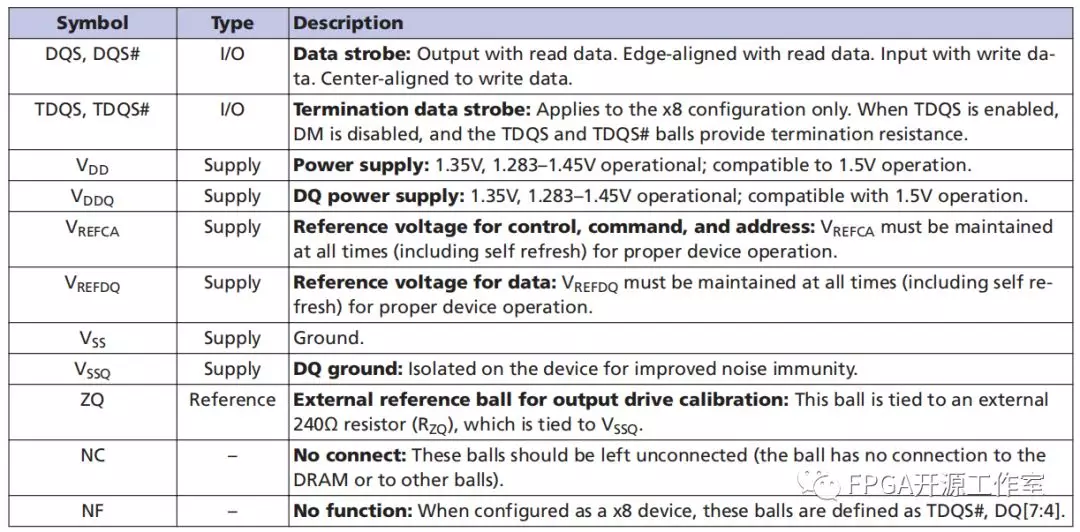

1.3接口

使用xilinx mig IP來控制DDR3的數(shù)據(jù)讀寫我們了解DDR3以上信息即可。 2 mig介紹

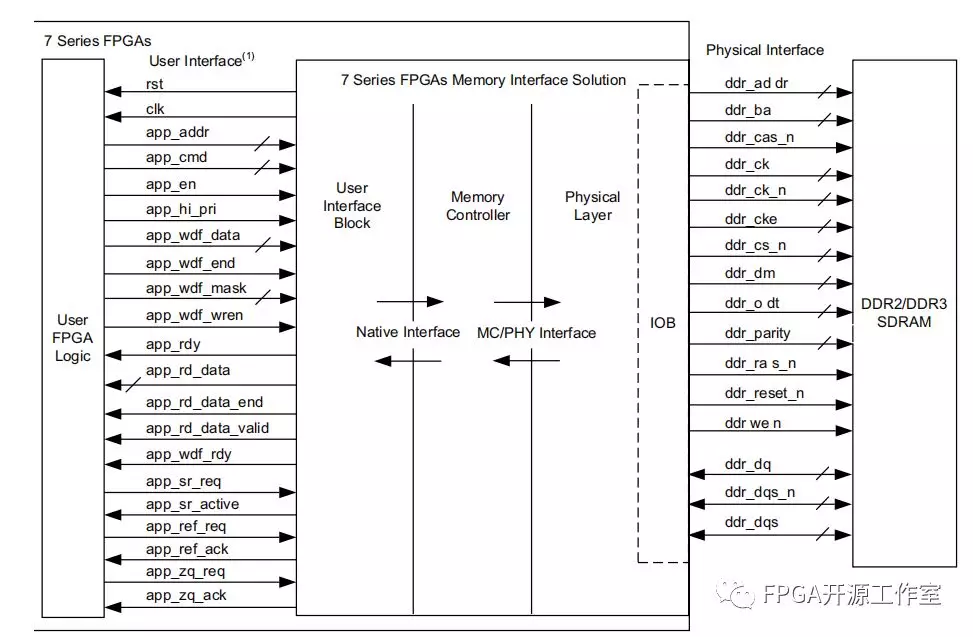

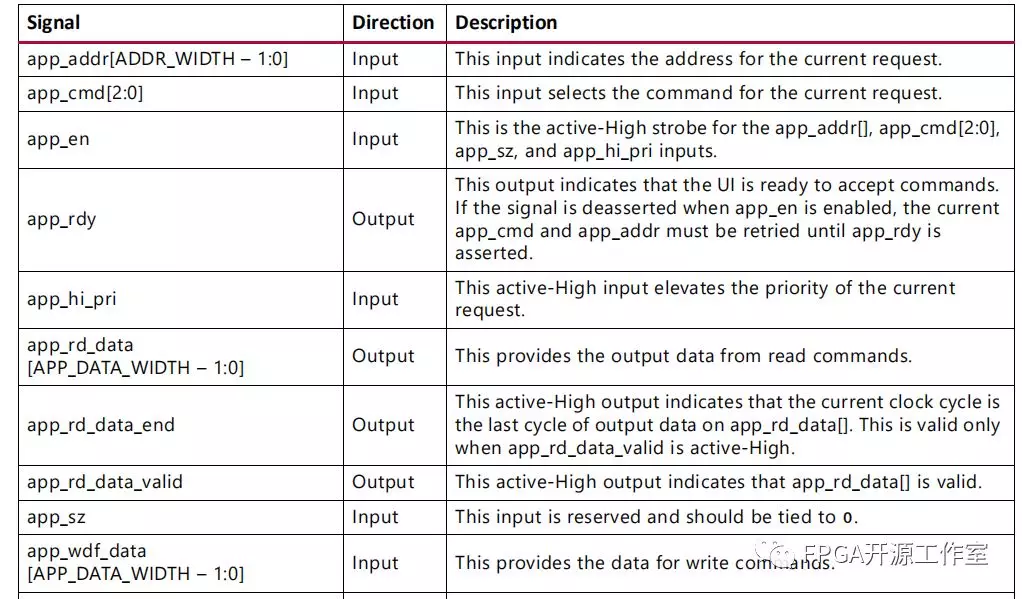

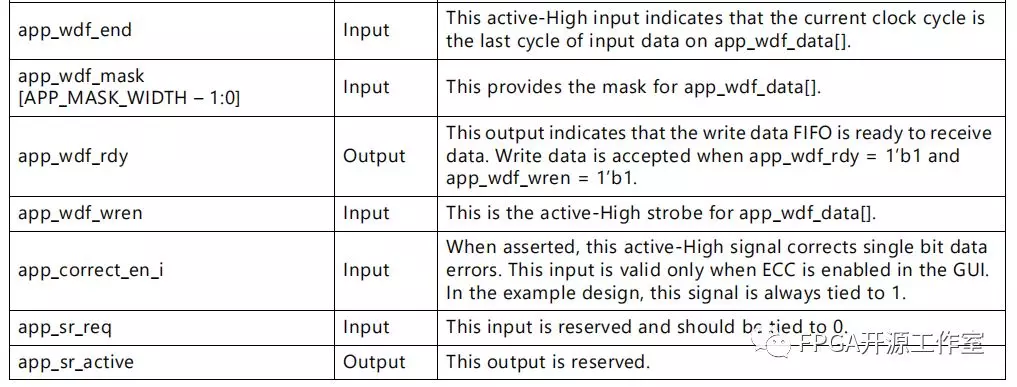

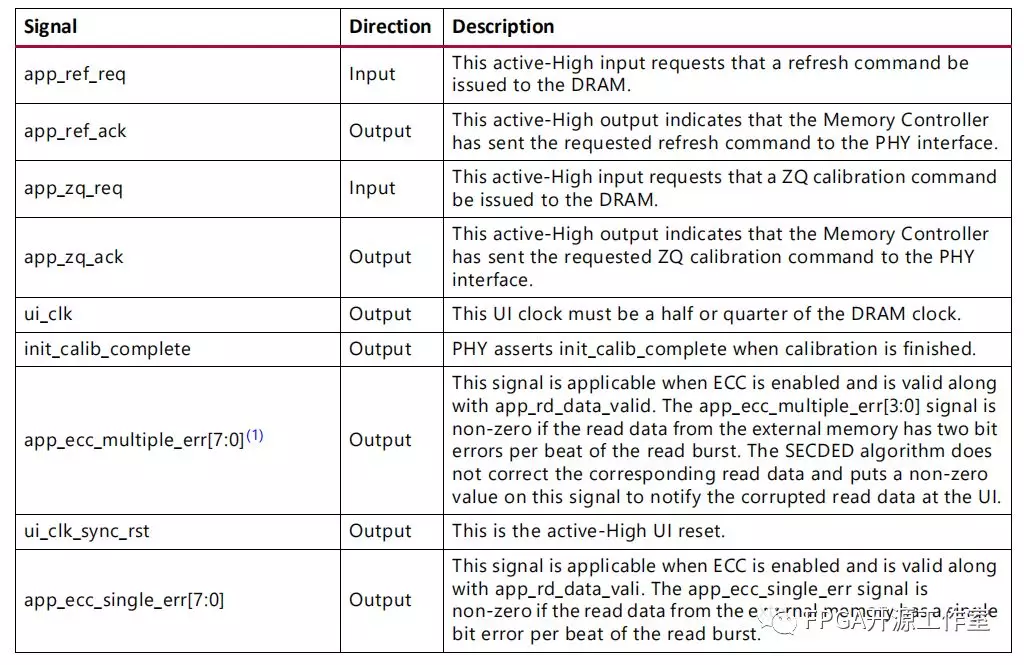

如上圖所示,mig(Memory Interface Solution) IP由三部分組成User Interface Block,Memory Controller和Physical Layer。IP的一邊是連接DDR3的接口(Physical Interface),另一邊是用戶邏輯控制接口(User FPGA Logic)。想要正確的控制DDR3的讀寫,我們需要正確的設(shè)置mig IP和正確的用戶邏輯控制接口邏輯。 2.1 mig user interface

對于mig用戶端接口含義我們將在《第三篇--mig IP用戶邏輯接口讀寫時序分析》中詳細(xì)介紹。 3 DDR3原理圖和FPGA原理圖

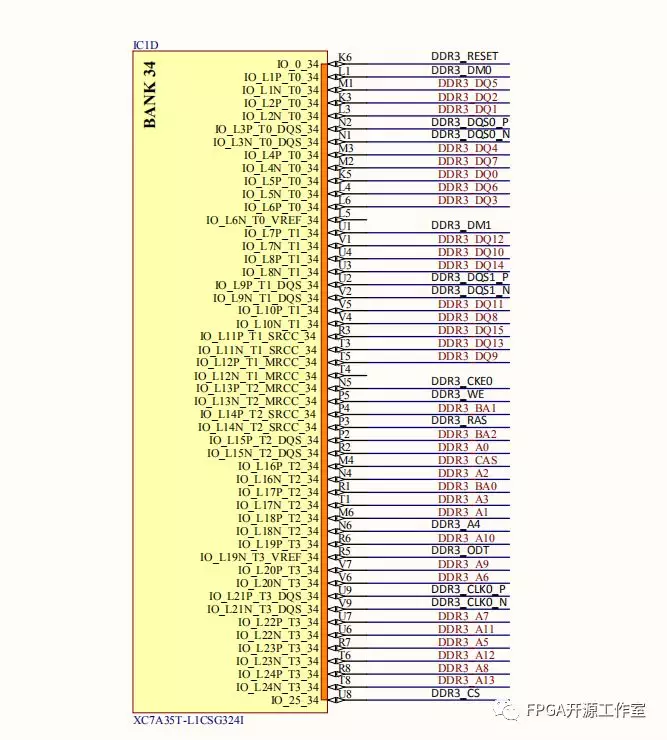

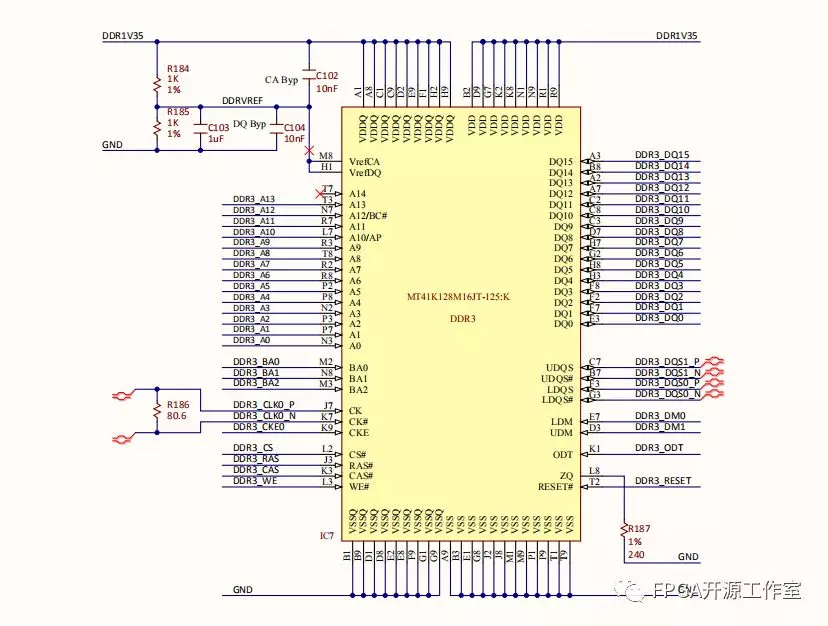

通過DDR3的原理圖我們可以知道DDR3的供電電壓為1.35V。DDR3掛在FPGA的34 bank上。 文章轉(zhuǎn)載自:?FPGA開源工作室 |

【本文地址】

| 今日新聞 |

| 推薦新聞 |

| 專題文章 |